大部份高速數(shù)位產(chǎn)品都使用時(shí)脈來(lái)進(jìn)行系統(tǒng)定時(shí)同步,在一個(gè)時(shí)脈周期中必須完成一系列作業(yè),包括一個(gè)邏輯深度內(nèi)的所有門(mén)切換時(shí)延、晶片內(nèi)部以及晶片之間的傳播時(shí)延、互連引起的上升時(shí)間或充電時(shí)延、設(shè)立和保持時(shí)間,以及時(shí)脈與數(shù)據(jù)線之間的偏差等等。定時(shí)預(yù)算負(fù)責(zé)給每個(gè)時(shí)延源分配時(shí)間。本文介紹在滿(mǎn)足功能要求的前提下,如何解決高速數(shù)位

PCB設(shè)計(jì)產(chǎn)品中定時(shí)預(yù)算、噪音預(yù)算和EMC測(cè)試要求所面臨的挑戰(zhàn)。

抖動(dòng)指的是從一個(gè)周期到下一個(gè)周期之間,時(shí)脈或數(shù)據(jù)沿到達(dá)時(shí)間的變化。訊號(hào)傳播時(shí)延源可能是隨機(jī)性的(當(dāng)這個(gè)抖動(dòng)無(wú)法預(yù)測(cè)時(shí)),也可能是確定性的(當(dāng)抖動(dòng)量大小能夠預(yù)測(cè)時(shí),如當(dāng)上升時(shí)間可與位周期相較時(shí)符號(hào)間干擾引起的抖動(dòng))。最后,PCB設(shè)計(jì)人員必須特定時(shí)預(yù)算增加一個(gè)‘裕量’,用來(lái)補(bǔ)償無(wú)法淮確預(yù)測(cè)的所有其他因素。不確定性越多,意味著需要越大的裕量來(lái)確保產(chǎn)品正確工作。

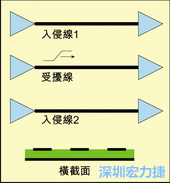

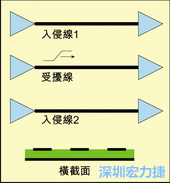

圖1:包含三個(gè)數(shù)據(jù)位的簡(jiǎn)單匯流排。

圖1:包含三個(gè)數(shù)據(jù)位的簡(jiǎn)單匯流排。

隨著時(shí)脈頻率的提高,時(shí)脈周期變得越來(lái)越短。PCB設(shè)計(jì)人員努力透過(guò)縮減定時(shí)預(yù)算中每個(gè)計(jì)畫(huà)的時(shí)間分配來(lái)達(dá)到更高的時(shí)脈頻率目標(biāo)。PCB設(shè)計(jì)人員越能淮確預(yù)計(jì)定時(shí)預(yù)算中的每項(xiàng)因素,需要的裕量就越小。裕量減少之后,相應(yīng)地就能允許在繼續(xù)滿(mǎn)足定時(shí)預(yù)算的前提下來(lái)縮短時(shí)脈周期。

有一種確定性抖動(dòng)是來(lái)自于匯流排中相鄰導(dǎo)線之間的串?dāng)_(即使在低損耗互連中也不例外)。采用能夠預(yù)測(cè)串?dāng)_的互連模型和一種能夠分析定時(shí)中串?dāng)_效應(yīng)的優(yōu)秀模擬器,PCB設(shè)計(jì)人員可以淮確預(yù)測(cè)串?dāng)_引起的確定性抖動(dòng),因而可以將抖動(dòng)預(yù)算降到最低并減少裕量。透過(guò)認(rèn)識(shí)串?dāng)_引起的抖動(dòng)來(lái)源,可以將其影響降到最低,并采取成本與性能之間的折衷,使最終產(chǎn)品實(shí)現(xiàn)最最佳化。

串?dāng)_引起的抖動(dòng)

當(dāng)某根數(shù)據(jù)位導(dǎo)線上訊號(hào)的到達(dá)時(shí)間受到相鄰數(shù)據(jù)位導(dǎo)線上同時(shí)出現(xiàn)訊號(hào)的影響時(shí),便會(huì)發(fā)生串?dāng)_引起的抖動(dòng)。

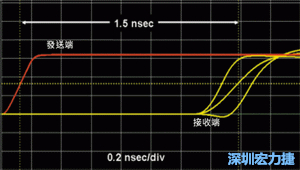

圖2:受擾線上訊號(hào)的到達(dá)時(shí)間與模擬條件有關(guān)。

例如,考察一條包含三個(gè)數(shù)據(jù)位的簡(jiǎn)單匯流排(圖1),每根數(shù)據(jù)位導(dǎo)線為一條9英寸長(zhǎng)的50歐姆表層線(線寬和間隔都是5mil)。這條匯流排的中央數(shù)據(jù)位線將成為受擾線。PCB設(shè)計(jì)人員可以在三種相應(yīng)的條件下模擬接收器端的訊號(hào)到達(dá)時(shí)間。可以模擬所有兩根‘入侵線’,即受擾線兩側(cè)的相鄰數(shù)據(jù)位線,分別讓它們停止傳輸訊號(hào)、傳輸與受擾線相同的數(shù)據(jù)位,或傳輸與受擾線相反的數(shù)據(jù)位訊號(hào)。模擬結(jié)果顯示,受擾線上訊號(hào)的到達(dá)時(shí)間與模擬條件有關(guān)(參見(jiàn)圖2)。當(dāng)其他數(shù)據(jù)位線停止傳輸訊號(hào)時(shí),總時(shí)延為1.5ns左右,而其他兩種條件下,根據(jù)匯流排上所傳輸?shù)臄?shù)據(jù)位模式,訊號(hào)的到達(dá)時(shí)間變化為±0.1ns,或者說(shuō)約為總時(shí)延的7%。

當(dāng)‘入侵線’與‘受擾線’驅(qū)動(dòng)同樣的數(shù)據(jù)位時(shí),受擾線上的時(shí)延增大。當(dāng)‘入侵線’上的數(shù)據(jù)位相反時(shí),受擾線上的時(shí)延減少。如果在定時(shí)預(yù)算中忽略了這種形式的確定性抖動(dòng),產(chǎn)品就有可能出現(xiàn)故障(或者必須將所需的裕量增大)。藕合的容性或感性電流加到安靜的導(dǎo)線上,將會(huì)影響到達(dá)時(shí)間和串?dāng)_引起的確定性抖動(dòng)。雖然遠(yuǎn)端串?dāng)_和串?dāng)_引起的確定性抖動(dòng)來(lái)源相同,但抖動(dòng)幅度與總串?dāng)_無(wú)關(guān),也與上升時(shí)間無(wú)關(guān)。訊號(hào)傳播速度的變化導(dǎo)致了串?dāng)_引起的確定性抖動(dòng),PCB設(shè)計(jì)人員可以透過(guò)仔細(xì)設(shè)計(jì)來(lái)將其消除。設(shè)計(jì)一個(gè)包含大量串?dāng)_,卻沒(méi)有確定性抖動(dòng)的系統(tǒng)是有可能的。

圖3:當(dāng)一條表層線導(dǎo)線與周?chē)鷮?dǎo)線距離較遠(yuǎn)且相互隔離時(shí),沿這條導(dǎo)線傳播的訊號(hào)的一些場(chǎng)線將僅僅分佈在導(dǎo)線材料內(nèi)部,而另一些場(chǎng)線則穿越空氣分佈在訊號(hào)與返迴路徑間。

確定性抖動(dòng)與訊號(hào)速度

95%以上的電路板使用FR4材料。訊號(hào)透過(guò)一條均質(zhì)傳輸線的傳播時(shí)延僅僅與訊號(hào)傳播時(shí)所面對(duì)的有效介電常數(shù)(kEFF)相關(guān)。如果kEFF約為3.5(FR4表層線中的kEFF可能就是這個(gè)值),則訊號(hào)的傳播速度大致為:12英寸/ns/=6.4英寸/ns。例如,一條9英寸長(zhǎng)導(dǎo)線的時(shí)延約為:長(zhǎng)度/6.4英寸/ns=9/6.4=1.4ns。如果再加上因2pF輸入門(mén)電容器引起的上升時(shí)間變長(zhǎng)而導(dǎo)致的0.1ns左右的時(shí)延,就得到了約1.5ns的總傳播時(shí)延。

由匯流排上位模式引起的kEFF的任何變化都將影響所有數(shù)據(jù)線上的訊號(hào)速度,而訊號(hào)速度影響傳播時(shí)延,反過(guò)來(lái)又會(huì)對(duì)抖動(dòng)產(chǎn)生影響。但相鄰訊號(hào)線上的位模式怎么會(huì)影響受擾線上訊號(hào)所面對(duì)的kEFF呢?答案全在于邊緣場(chǎng)線。

當(dāng)一條表層線導(dǎo)線與周?chē)鷮?dǎo)線距離較遠(yuǎn)且相互隔離時(shí)(圖3),沿這條導(dǎo)線傳播的訊號(hào)的一些場(chǎng)線將僅僅分佈在導(dǎo)線材料內(nèi)部,而另一些場(chǎng)線則穿越空氣分佈在訊號(hào)與返迴路徑之間。延伸到導(dǎo)線寬度之外的場(chǎng)線稱(chēng)為邊緣場(chǎng)線。在一條50歐姆的FR4表層線中,訊號(hào)與返迴路徑之間的電容器約有一半是由邊緣場(chǎng)引起的。

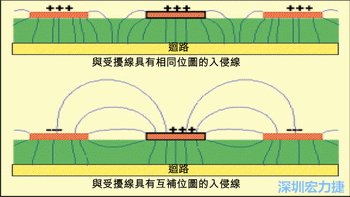

圖4:不同邊緣場(chǎng)的分佈。

相鄰入侵訊號(hào)線的存在會(huì)影響受擾線的邊緣場(chǎng)分佈,具體情況取決于入侵線上的位模式。當(dāng)兩根入侵線攜帶與受擾線相同的數(shù)據(jù)位時(shí),所有三條訊號(hào)線上的電壓相同,導(dǎo)線上方空氣中的邊緣場(chǎng)線很少。

當(dāng)相鄰入侵線上的數(shù)據(jù)位與受擾線上的數(shù)據(jù)位相反時(shí),受擾線與入侵線之間有很大壓差,并且存在許多邊緣場(chǎng)。受擾線到返迴路徑之間場(chǎng)線的分量越大(空氣中的場(chǎng)線與導(dǎo)線材料中的場(chǎng)線相較),kEFF就越小。這些不同邊緣場(chǎng)的分佈如圖4所示。

當(dāng)入侵線上的位模式與受擾線相同時(shí),后者面對(duì)的kEFF增大,這將導(dǎo)致傳播速度降低,時(shí)延變長(zhǎng)。當(dāng)入侵線上的位模式與受擾線相反時(shí),受擾線上的kEFF減少,傳播速度提高,時(shí)延變短。在前述的例子中,由于三條數(shù)據(jù)位線之間的藕合非常緊密,邊緣場(chǎng)與kEFF變化引起的確定性抖動(dòng)達(dá)±0.1ns(總時(shí)延為1.5ns)。

圖5:對(duì)于受擾線的場(chǎng)線來(lái)說(shuō),介電系數(shù)一樣,都等于導(dǎo)線條帶的介電常數(shù)。

將確定性抖動(dòng)降到最低

降低串?dāng)_導(dǎo)致的確定性抖動(dòng)的一種途徑是透過(guò)加大導(dǎo)線之間的間隔來(lái)降低邊緣場(chǎng)的覆蓋程度。例如,透過(guò)將導(dǎo)線間隔增大到線寬的兩倍(這是為獲得可接受的近端串?dāng)_而采取的一個(gè)常用設(shè)計(jì)規(guī)則),在總時(shí)延為1.5ns的情況下,可將確定性抖動(dòng)降低到60ps以下,即總時(shí)延的4%。

減少受擾線與入侵線之間的間隔不僅會(huì)導(dǎo)致確定性抖動(dòng),還會(huì)引起串?dāng)_問(wèn)題。為了降低串?dāng)_和抖動(dòng),導(dǎo)線間隔應(yīng)盡可能加大,或至少兩倍于線寬。但是,這種方法意味著降低印刷電路板的密度(可能導(dǎo)致成本增加)。PCB設(shè)計(jì)人員需要一種EDA工具來(lái)淮確預(yù)計(jì)串?dāng)_和確定性抖動(dòng),以評(píng)估成本與性能之間的折衷。一個(gè)整合二維場(chǎng)解決方案的模擬器不僅要自動(dòng)考慮噪音效應(yīng),而且還應(yīng)該將與串?dāng)_相關(guān)的確定性抖動(dòng)納入考慮。

消除確定性抖動(dòng)

空氣中邊緣場(chǎng)的變化引起串?dāng)_導(dǎo)致的確定性抖動(dòng)時(shí),在同質(zhì)介電分佈結(jié)構(gòu)中將不會(huì)發(fā)生任何確定性的抖動(dòng),例如完全內(nèi)嵌的表層線或帶狀線。在一個(gè)帶狀線幾何中,受擾線與入侵線之間的邊緣場(chǎng)可能發(fā)生緊密的相互作用,但無(wú)論邊緣場(chǎng)如何分佈,對(duì)于受擾線的場(chǎng)線來(lái)說(shuō),介電系數(shù)一樣,都等于導(dǎo)線條帶的介電常數(shù)(圖5)。

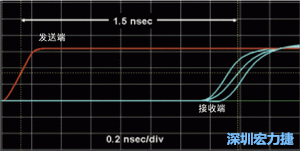

圖6:入侵線無(wú)訊號(hào)、入侵線位模式與受擾線相同及相反三種情形下對(duì)受擾訊號(hào)到達(dá)時(shí)間的模擬結(jié)果。

對(duì)于極端情況,當(dāng)導(dǎo)線間隔等于50歐姆帶狀線中的線寬時(shí),kEFF總是等于導(dǎo)線材料的介電常數(shù),而與入侵線上的位模式無(wú)關(guān)。當(dāng)位模式改變時(shí),受擾線上沒(méi)有抖動(dòng)。圖6顯示了入侵線無(wú)訊號(hào)、入侵線位模式與受擾線相同及相反三種情形下對(duì)受擾訊號(hào)到達(dá)時(shí)間的模擬結(jié)果。雖然受擾線上出現(xiàn)大量串?dāng)_電壓,但受擾線上訊號(hào)的到達(dá)時(shí)間沒(méi)有發(fā)生抖動(dòng)。

在定時(shí)嚴(yán)格的設(shè)計(jì)中,PCB設(shè)計(jì)人員可以將所有對(duì)定時(shí)感應(yīng)的訊號(hào)線佈設(shè)在掩埋的帶狀線層中,以消除抖動(dòng)的一個(gè)來(lái)源,并降低所需的總定時(shí)預(yù)算。在選擇整合有二維場(chǎng)解決方案的模擬器時(shí),應(yīng)該選擇一種自動(dòng)將噪音以及與串?dāng)_相關(guān)的確定性抖動(dòng)納入考慮的工具。

深圳宏力捷推薦服務(wù):PCB設(shè)計(jì)打樣 | PCB抄板打樣 | PCB打樣&批量生產(chǎn) | PCBA代工代料