目前的交換式穩(wěn)壓器和電源設(shè)計更精巧、性能也更強(qiáng)大,但其面臨的挑戰(zhàn)之一,在于不斷加速的開關(guān)頻率使得PCB設(shè)計更加困難。PCB布局正成為區(qū)分一個開關(guān)電源設(shè)計好壞的分水嶺。本文將就如何在第一次就實現(xiàn)良好PCB布局提出建議。

以一個將24V降為3.3V的3A交換式穩(wěn)壓器為例。乍看之下,一個10W穩(wěn)壓器不會太困難,所以

PCB設(shè)計師通常會忍不住直接進(jìn)入建構(gòu)階段。

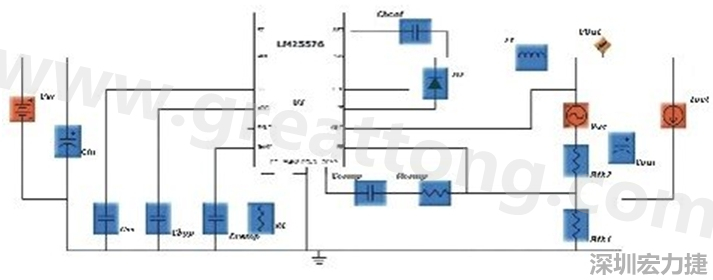

不過,在采用像美國國家半導(dǎo)體的Webench等設(shè)計軟件后,我們可觀察該構(gòu)想實際上會遭遇哪些問題。輸入上述要求后,Webench會選出該公司‘Simpler Switcher’系列的LM25576(一款包括3A FET的42V輸入元件)。它采用的是帶散熱墊的TSSOP-20封裝。

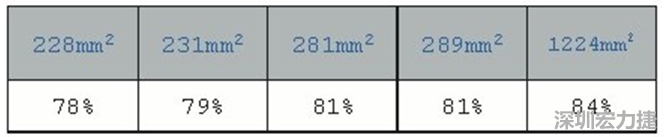

Webench選項包括對體積或效率的設(shè)計最佳化,這些均為單一選項。即高效率要求低開關(guān)頻率(降低FET內(nèi)的開關(guān)損耗)。因此需要大容量的電感和電容,因而需更大PCB空間。

注意:最高效率是84%,且此最高效率是當(dāng)輸入-輸出間的壓差很低時實現(xiàn)的。此例中,輸入/輸出比率大于7。一般情況,用兩個級降低級-級比率,但透過兩個穩(wěn)壓器得到的效率不會更好。

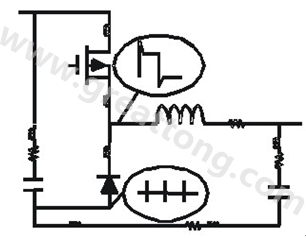

接著,我們選擇最小PCB面積的最高開關(guān)頻率。高開關(guān)頻率最可能在布局方面產(chǎn)生問題。隨后Webench產(chǎn)生包含所有主動和被動元件的電路圖。

電路設(shè)計

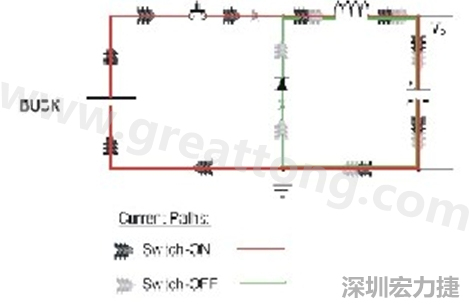

參考圖1的電流通路:把FET在導(dǎo)通狀態(tài)下流經(jīng)的通路標(biāo)記為紅色;把FET在關(guān)斷狀態(tài)下的迴路標(biāo)記為綠色。我們觀察到兩種不同情況:兩種顏色區(qū)域和僅一種顏色的區(qū)域。我們必須特別關(guān)注后一種情況,因為此時電流在零以及滿量程電壓間交替變化。這些均為高di/dt區(qū)域。

圖1

高di/dt的交流電在PCB導(dǎo)線周圍產(chǎn)生大量磁場,該磁場是該電路內(nèi)其他元件甚至同一或鄰近PCB上其他電路的主要干擾源。由于假設(shè)公共電流路徑不是交流電,因此它不是關(guān)鍵路徑,di/dt的影響也小得多。另一方面,隨著時間變化,這些區(qū)域的負(fù)載更大。本例中,從二極體陰極到輸出以及從輸出地到二極體陽極是公共通路。當(dāng)輸出電容充放電時,該電容具有極高的di/dt。連接輸出電容的所有線路必須滿足兩個條件:由于電流大,它們要寬;為最小化di/dt影響,它們必須盡量短。

圖2

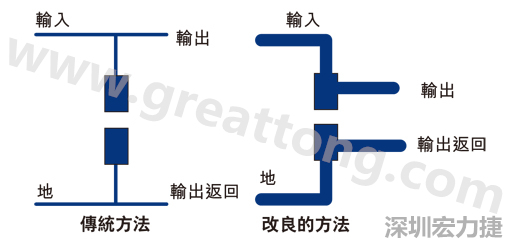

事實上,PCB設(shè)計師不應(yīng)采用把導(dǎo)線從Vout和接地引至電容的所謂傳統(tǒng)布局方法。這些導(dǎo)線應(yīng)是流經(jīng)大交流電的。將輸出和接地直接連至電容端子是更好的方法。因此,交替變化的電流僅展現(xiàn)在電容上。連接電容的其他導(dǎo)線現(xiàn)在流經(jīng)的幾乎是恒定電流,且與di/dt相關(guān)的任何問題都已被解決。

圖3

接地是另一個經(jīng)常發(fā)生誤解之處。簡單地在‘level 2’放置一個地平面并將全部接地連接連至其上并不會獲得好的結(jié)果。

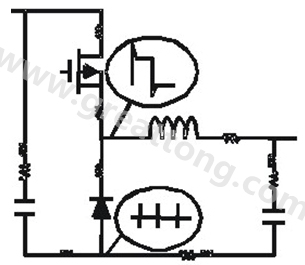

圖4

讓我們看看為什么。我們的設(shè)計范例顯示,有高達(dá)3A的電流必須從接地流回到源端(一個24V汽車電池或一個24V電源)。在二極體、COUT、CIN和負(fù)載的接地連接處會有大電流。而交換式穩(wěn)壓器的接地連接流經(jīng)的電流小。同樣情況也適用于電阻分壓器的接地參考。若上述全部接地接腳都連至一個地平面,我們會遇到接地彈跳(ground bouncing)。雖然很小,但電路中的感應(yīng)點(如藉以獲得反饋電壓的電阻分壓器)將不會有穩(wěn)定的參考接地。這樣,整個穩(wěn)壓精密度將受到極大影響。實際上,我們甚至?xí)碾[藏在level 2的地平面中得到‘震鈴(ringing)’,而該震鈴非常難以定位。

圖5

另外,大電流連接必須用到連接地平面的過孔,而過孔是另一個干擾和雜訊源。把CIN接地連接作為電路輸入和輸出側(cè)所有大電流接地導(dǎo)線的星節(jié)點是更好的方案。星節(jié)點連接地平面及兩個小電流接地連接(IC和分壓器)。

圖6

現(xiàn)在地平面很潔淨(jìng):沒有大電流、沒有地彈跳。所有大電流地是以星型與CIN地連接起來的。所有PCB設(shè)計師必須做的是使接地導(dǎo)線(全部在PCB的第一層)盡可能短而粗。在這種背景下,若節(jié)省銅,基本上不會獲得好結(jié)果。

節(jié)點阻抗

應(yīng)檢查高阻抗節(jié)點,因為它們很容易被干擾。

最關(guān)鍵節(jié)點是IC的反饋接腳,其訊號取自電阻分壓器。FB接腳是放大器(如LM25576)或比較器的輸入(如采用磁滯穩(wěn)壓器的場合)。在兩種情況,F(xiàn)B點的阻抗都相當(dāng)高。因此,電阻分壓器應(yīng)放置在FB接腳的右側(cè),從電阻分壓器中間連一條短導(dǎo)線到FB。從輸出到電阻分壓器的導(dǎo)線是低阻抗,且可用較長導(dǎo)線連至電阻分壓器。此處的重點是布線方法而非導(dǎo)線長度。

其他節(jié)點就不是如此關(guān)鍵了。所以不必憂慮開關(guān)節(jié)點、二極體、COUT、開關(guān)IC的VIN接腳或CIN。

布線技巧

布線手法會為電阻分壓器帶來差別。該導(dǎo)線從COUT連至電阻分壓器,其接地回到COUT。我們必須確保該迴路不會形成一個開放區(qū)域。開放區(qū)域會產(chǎn)生接收天線的作用。若我們能保證導(dǎo)線下的地平面是沒被干擾的,則由導(dǎo)線和其下的接地以及l(fā)evel 1和level 2間形成的區(qū)域應(yīng)是不受干擾的。現(xiàn)在,我們可得知為何接地不應(yīng)放在level 4,因為距離顯著增加了。

另一種方式是電阻分壓器的地連接可布線至level 1,使兩條導(dǎo)線平行并盡可能靠近以使區(qū)域更小。這些觀察適用于訊號流經(jīng)的全部導(dǎo)線:感測器連接、放大器輸出、ADC或音訊功率放大器的輸入。對每個類比訊號,都要處理得使其不太容易導(dǎo)入雜訊。

只要有可能,就盡量最小化開放區(qū)域的這個要求,對低阻抗導(dǎo)線也同樣適用;在這種情況下,我們有一個向PCB其他部份或其他設(shè)備發(fā)射干擾訊號的潛在源(天線)。注意:就開放區(qū)域來說是越小越好。

以下兩條導(dǎo)線也很關(guān)鍵:從IC的開關(guān)輸出到二極體和電感節(jié)點;從二極體到該節(jié)點。這兩條導(dǎo)線都有很高的di/dt:無論是開關(guān)導(dǎo)通還是二極體流過電流,所以這些導(dǎo)線應(yīng)盡可能短而粗。從節(jié)點到電感以及從電感到COUT的導(dǎo)線就不那么關(guān)鍵。在本例中,電感電流相對恒定且變化緩慢。我們所要做的是確保它是低阻抗點以最小化壓降。

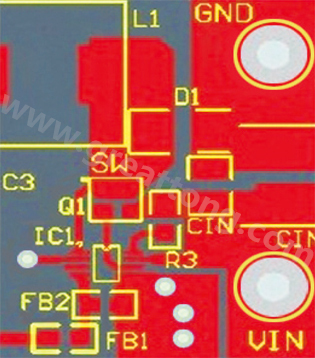

實際布局

我們看一下好的布局(下面)。主要元件是一款與外接FET一起使用的MSOP-8封裝控制器。

觀察CIN附近的空間。注意:該電容的接地點直接連至二極體陽極。你無法使‘電源地’內(nèi)的導(dǎo)線過短!FET[SW]應(yīng)向上移動幾毫米以縮短陰極-電感-FET導(dǎo)線。

COUT區(qū)域是看不到的。但我們可觀察到電阻分壓器(FB1-FB2)非常接近該IC。FB2與另一個地平面連接,IC的地接腳也一樣處理。利用三個過孔把‘訊號’地連至地平面,而‘電源’地也是利用三個過孔連接PCB的GND接腳。這樣,‘訊號’地就不會‘看’到‘電源’地的任何接地彈跳。

若你遵循幾個簡單規(guī)則(本文僅討論了其中一些),則你的PCB布局將不會遇到麻煩。在動手布局前,仔細(xì)思考PCB布局將事半功倍,有助于節(jié)省處理開關(guān)電源異常所需花費的時間。

深圳宏力捷推薦服務(wù):PCB設(shè)計打樣 | PCB抄板打樣 | PCB打樣&批量生產(chǎn) | PCBA代工代料