電子設(shè)備在使用及設(shè)計上的安全性規(guī)范不斷更新,使得電震隔離器(galvanic isolator)幾乎成為所有資料擷取及資料傳輸系統(tǒng)的必備元件。感應(yīng)器及致動器內(nèi)潛藏著危險的高壓電,若要將控制系統(tǒng)的低電壓電路從中隔離出來,使用數(shù)位隔離器是其中一種方法。

為了簡化隔離系統(tǒng)的

PCB設(shè)計,本文將說明電容式數(shù)位隔離器的基本功能與隔離器在訊號路徑中的位置,并且提供能成功設(shè)計出電路板的重要建議。

基本功能

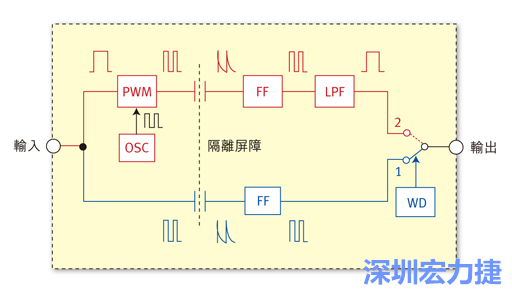

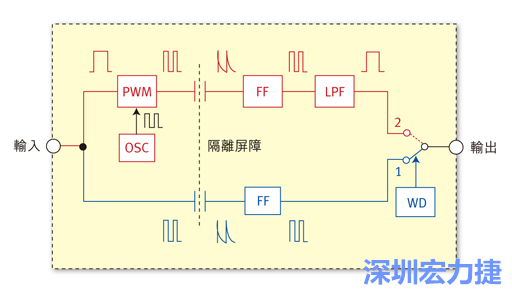

圖1為電容式數(shù)位隔離器的簡明示意圖,其中包含一個高速及一個低速的訊號路徑。高速路徑(藍色)傳輸介于100kbps至150Mbps的訊號,而低速路徑(橘色)則傳輸介于100kbps至DC的訊號。

圖1:電容式數(shù)位隔離器簡明示意圖。

藍色路徑中處理的高速訊號會被電容式隔離障礙界定為快速暫態(tài),后續(xù)的正反器(FF)會接著將暫態(tài)轉(zhuǎn)換成與輸入訊號同形狀、同相位的脈沖,而內(nèi)部監(jiān)視計時器(WD)則會檢查高速訊號邊緣的固定出現(xiàn)次數(shù)。對于低頻率輸入訊號,連續(xù)訊號邊緣的持續(xù)時間會超出監(jiān)視計時視窗之外,這使得監(jiān)視計時器必須將輸出切換的位置從高速路徑(位置1)變換至低速路徑(位置2)。

低速路徑處理的功能元件比高速路徑多。由于低頻率輸入訊號需要隔離障礙才能承受大電容,因此輸入訊號被用來對內(nèi)部震蕩器(OSC)的載波頻率進行脈沖寬度調(diào)變(PWM)。這會創(chuàng)造出夠高的頻率,以便通過電容障礙。由于輸入已經(jīng)過調(diào)整,因此需要低通濾波器(LPF)來移除實際資料的高頻率載波,防止此載波傳導(dǎo)至輸出。

訊號鏈中的位置

數(shù)位隔離器分為單通道、雙通道、三通道及四通道裝置等型制,可用于單向及雙向操作。其中的共通點包括:未遵循任何特定介面標(biāo)淮;使用3V/5V邏輯切換技術(shù);僅能利用電流來隔離數(shù)位單端(SE)資料線路。

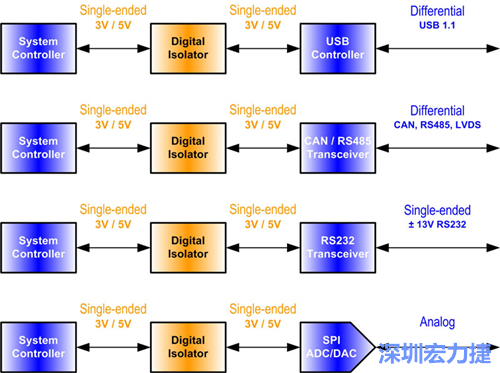

最后一點可說是設(shè)計方面的限制,圖2顯示如何隔離低電壓SPI、高電壓RS232、差動USB及差動CAN/RS485等多種介面,不過,所有介面都需要將數(shù)位隔離器放置在隔離介面的單端3V/5V部分中。

圖2:數(shù)位隔離器必須放置在隔離介面的單端部分中。

由于數(shù)位隔離器的升高與降低時間為1至2奈秒,所以長訊號線很可能出現(xiàn)訊號反射,原因是長訊號跡線的特性阻抗不符合隔離器輸出的來源阻抗。因此,建議將隔離器放置在其對應(yīng)資料槽與控制器、驅(qū)動器、接收器與收發(fā)器等資料來源的附近。對于無法做此配置的設(shè)計,則必須使用控制的阻抗傳輸線。

PCB設(shè)計要點

針對數(shù)位電路板,請使用標(biāo)淮FR-4環(huán)氧玻璃做為PCB材質(zhì),因為這種材質(zhì)符合UL94-V0需求,而且相較于低成本的材質(zhì),它能夠減少高頻率下的介電受損、降低濕度吸收、增加強度及硬度,并在可燃性方面提高自行熄滅的能力。

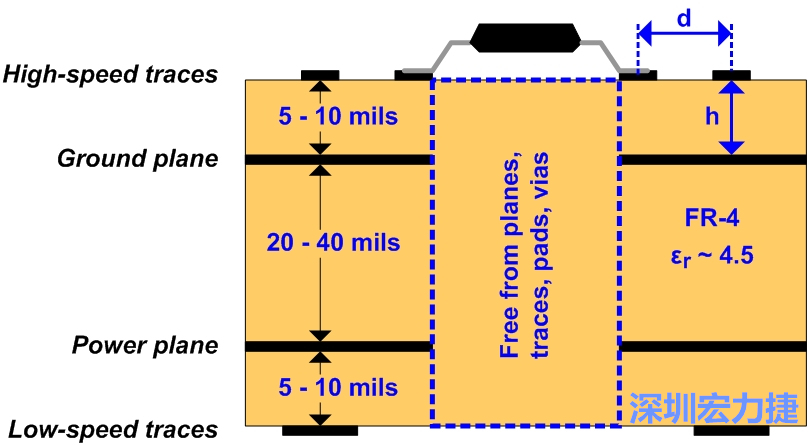

為了完成低EMI PCB設(shè)計,建議至少使用四層堆迭(圖3),其由上至下的堆迭順序如下:高速訊號層、接地平面、電源平面及低頻率訊號層。

圖3:建議的四層堆迭。

分布在頂層的高速訊號跡線能夠確實連接隔離器及對應(yīng)的驅(qū)動器,而且必須將訊號跡線的長度縮短,并避免使用過孔,進而將跡線電感降至最低。

在高速訊號層下加入固定接地平面可確實達到接地層及訊號跡線之間的電藕合,這會對傳輸線路間的相互連接產(chǎn)生控制的阻抗,并且大幅減少電磁干擾(EMI),而且固定接地平面可以做為回流電流的絕佳低電感路徑。

在接地平面下加入電源平面,這兩個參考平面可額外產(chǎn)生大約100pF/in2的高頻率旁路電容。

在底層進行低速控制訊號的布線,這些訊號連結(jié)有足夠的容限可承受過孔造成的中斷,因此可達到更大的彈性。

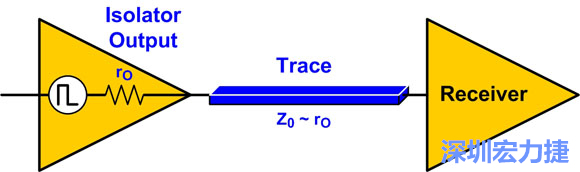

控制的阻抗傳輸線都是具備特性阻抗Z0的跡線,而Z0深受其形狀影響。對于超過15公厘(收發(fā)訊號時間為1奈秒)及超過30公厘(收發(fā)訊號時間為2奈秒)的跡線,跡線阻抗必須符合隔離器的輸出阻抗Z0至rO(圖4),才能將訊號反射降至最低,這稱為來源阻抗匹配。

圖4:來源阻抗匹配:Z0至rO。

針對隔離器資料表所示的電壓電流輸出特性,使用與其相當(dāng)接近的線性區(qū)段,即可決定隔離器的動態(tài)輸出阻抗r0。根據(jù)經(jīng)驗法則,一般的輸出阻抗約為70Ω,因此,對于2盎司鍍銅的標(biāo)淮跡線厚度及4.5的FR-4介電來說,寬8公厘、高10公厘并位于接地平面上的跡線可產(chǎn)生必備的70Ω特性阻抗。

布線要點

為了維持訊號的完整性及低EMI,下列是幾項關(guān)于布線的主要建議要點。

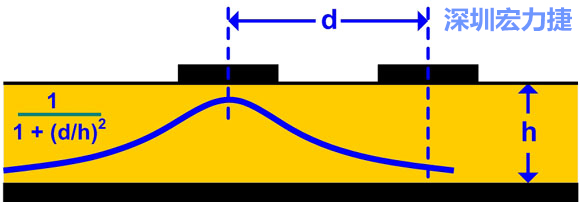

為了將串音(crosstalk)降至10%以下,務(wù)必將訊號跡線彼此隔開,并保持其間距為訊號跡線至接地高度的3倍(d=3h)。由于訊號跡線的回流電流密度如1/[1+(d/h)2]函式所示,因此在密度到達d>3h時便會低到足以避免鄰近的跡線出現(xiàn)明顯的串音(圖5)。

圖5:藉由d=3h將串音降至最低。

使用45°跡線彎曲(或倒角角隅)而非90°彎曲可維持有效的跡線阻抗,并避免訊號反射。

若要在雜訊極大的環(huán)境中運作,請將隔離器的未使用致能輸入穿過電阻(1kΩ至10kΩ)再連接至適當(dāng)?shù)膮⒖计矫妗A硗猓瑢⒏哂行?active-high)高致能輸入連接至電源平面,并且將低有效輸入連接至接地平面。

避免使用快速調(diào)節(jié)的訊號跡線來變換各層,因為過孔電感會增加訊號路徑的電感。

在隔離器及周圍電路之間使用短訊號跡線可避免雜訊夾帶的情形。數(shù)位隔離器通常會搭配獨立的DC/DC轉(zhuǎn)換器,以便供應(yīng)能跨越隔離障礙的電源。由于隔離器的單端傳輸訊號對于雜訊夾帶相當(dāng)敏感,所以長訊號線很容易就會夾帶鄰近DC/DC轉(zhuǎn)換器的切換雜訊。

將大量電容(亦即10μF)設(shè)置在電壓穩(wěn)壓器之類的供電來源附近,或設(shè)置在電源進入PCB的位置。

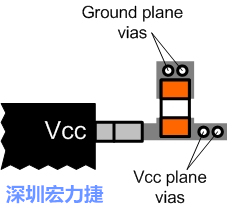

在裝置中放置較小的0.1μF或0.01μF旁路電容,方法是將電容的電源端直接連接至裝置的供電端子,然后穿過過孔連接至Vcc平面。另外,將電容的接地端穿過過孔,然后連接至接地平面(圖6)。

圖6:將旁路電容直接連接Vcc端子。

使用多個過孔來連接旁路電容及其他防護裝置,例如暫態(tài)電壓消除器及Zener二極體,可將接地連結(jié)的過孔電感降至最低。

深圳宏力捷推薦服務(wù):PCB設(shè)計打樣 | PCB抄板打樣 | PCB打樣&批量生產(chǎn) | PCBA代工代料