本文闡述了近來

PCB設(shè)計(jì)工程師們所面臨的挑戰(zhàn),文中探討了如何迎接這些挑戰(zhàn)及潛在的解決方案;此外,文中同時(shí)以明導(dǎo)的PCB評(píng)估套裝軟件為例,描述了如何解決PCB設(shè)計(jì)軟件的評(píng)估問題。

作為研發(fā)人員,主要的考量是如何將最新的先進(jìn)技術(shù)整合在產(chǎn)品中。這些先進(jìn)技術(shù)既可以展現(xiàn)在卓越的產(chǎn)品功能上,也必須能展現(xiàn)在降低產(chǎn)品成本上,困難在于如何將這些技術(shù)有效地應(yīng)用在產(chǎn)品中。有許多因素需要考慮,產(chǎn)品上市的時(shí)間是最為重要的因素之一,且圍繞產(chǎn)品上市時(shí)間,有許多決定是在不斷更新的。

在這個(gè)前提下,必須考慮的因素很廣泛,從產(chǎn)品功能、設(shè)計(jì)實(shí)現(xiàn)、產(chǎn)品測(cè)試以及電磁干擾(EMI)是否符合要求均包含在內(nèi)。減少設(shè)計(jì)反覆是可能的,但這必須仰賴前期工作的完成情況。大多數(shù)時(shí)候,越是到產(chǎn)品設(shè)計(jì)后期越容易發(fā)現(xiàn)問題,更為痛苦的是要針對(duì)發(fā)現(xiàn)的問題進(jìn)行更改。

然而,盡管許多人都清楚這個(gè)經(jīng)驗(yàn)法則,但實(shí)際情況卻是另外一種場(chǎng)景,即許多公司都很清楚,擁有一個(gè)高整合度的設(shè)計(jì)軟件非常重要,但這個(gè)想法卻往往受限于高昂的價(jià)格。本文將闡述PCB設(shè)計(jì)所面臨的挑戰(zhàn),以及作為一名PCB設(shè)計(jì)者在評(píng)估一款PCB設(shè)計(jì)工具時(shí)該考慮哪些因素。

以下是PCB設(shè)計(jì)者必須考量并影響其決定的幾點(diǎn)因素:

1. 產(chǎn)品功能

a.覆蓋基本要求的基本功能,包括:原理圖與PCB布局之間的互動(dòng);自動(dòng)扇出布線、推拉等布線功能,以及基于設(shè)計(jì)規(guī)則約束的布線能力;精確的DRC校驗(yàn)器。

b.當(dāng)公司從事一個(gè)更為復(fù)雜的設(shè)計(jì)時(shí)升級(jí)產(chǎn)品功能的能力,如:高密度互連(HDI)介面;靈活設(shè)計(jì);嵌入被動(dòng)元件;射頻(RF)設(shè)計(jì);自動(dòng)腳本產(chǎn)生;拓樸布局布線;可制造性(DFM)、可測(cè)試性(DFT)及可生產(chǎn)性(DFF)等。

c.附加產(chǎn)品能執(zhí)行類比模擬、數(shù)位模擬、類比數(shù)位混合訊號(hào)模擬、高速訊號(hào)模擬以及RF模擬。

d.具備一個(gè)易于制作和管理的中央元件庫(kù)。

2. 優(yōu)秀的伙伴

一個(gè)技術(shù)上位于業(yè)界領(lǐng)導(dǎo)層中并較其他廠商傾注了更多心血的良好伙伴,可助你在最短的時(shí)間內(nèi)設(shè)計(jì)出具有最大功效和具有領(lǐng)先技術(shù)的產(chǎn)品。

3. 投資報(bào)酬率

價(jià)格應(yīng)該是上述因素中最為次要的考慮因素,必須更加關(guān)注投資報(bào)酬率。

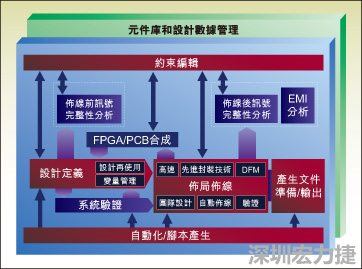

圖1:從前端到后端的一個(gè)典型整合系統(tǒng)設(shè)計(jì)流。

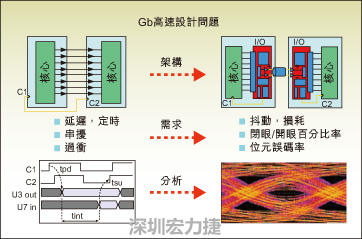

圖2:平行匯流排和串并轉(zhuǎn)換設(shè)計(jì)所遇到的典型設(shè)計(jì)問題。

PCB評(píng)估需考慮許多因素。設(shè)計(jì)者要尋找的開發(fā)工具類型取決于他們所從事的設(shè)計(jì)工作復(fù)雜性。由于系統(tǒng)正趨于越來越復(fù)雜,實(shí)體走線和電氣元件布放的控制發(fā)展愈來愈廣泛,以至于必須為設(shè)計(jì)過程中的關(guān)鍵路徑設(shè)定約束條件。但是,過多的設(shè)計(jì)約束卻束縛了設(shè)計(jì)靈活性。設(shè)計(jì)者們務(wù)必良好瞭解其設(shè)計(jì)及規(guī)則,如此才能清楚要在何時(shí)使用這些規(guī)則。

圖1顯示了一個(gè)由前端到后端的標(biāo)淮合成系統(tǒng)設(shè)計(jì)。它始于設(shè)計(jì)定義(原理圖輸入),該設(shè)計(jì)定義與約束編輯緊密集合在一起。在約束編輯中,設(shè)計(jì)者既可定義實(shí)體約束又可定義電氣約束。電氣約束將為網(wǎng)路驗(yàn)證驅(qū)動(dòng)模擬器進(jìn)行布局前和布局后分析。仔細(xì)看看設(shè)計(jì)定義,它還與FPGA/PCB整合相鏈接。FPGA/PCB整合的目的是為了提供雙向整合、數(shù)據(jù)管理和在FPGA與PCB之間執(zhí)行協(xié)同設(shè)計(jì)能力。

在布局階段輸入了與設(shè)計(jì)定義期間相同的用于實(shí)體實(shí)現(xiàn)的約束規(guī)則。這就減少了從文件到布局過程中出錯(cuò)的概率。接腳交換、邏輯閘交換、甚至輸入輸出介面組(IO_Bank)交換均需返回到設(shè)計(jì)定義階段進(jìn)行更新,因此各個(gè)環(huán)節(jié)的設(shè)計(jì)是同步的。

評(píng)估期間,設(shè)計(jì)者必須問自己:對(duì)他們而言,什么標(biāo)淮是至關(guān)重要的?

讓我們看看一些迫使設(shè)計(jì)者重新審視其現(xiàn)有開發(fā)工具功能并開始訂購(gòu)一些新功能的趨勢(shì):

1.HDI

半導(dǎo)體復(fù)雜性和邏輯閘總量的增加已要求積體電路具有更多的接腳及更精細(xì)的接腳間距。在一個(gè)接腳間距為1mm的BGA元件上設(shè)計(jì)2,000個(gè)以上的接腳在目前已是很平常的事情,更不要說在接腳間距為0.65mm的元件上布放296個(gè)接腳了。越來越快的上升時(shí)間和訊號(hào)完整性(SI),正在要求更多的電源和接地接腳,故需要占用多層板中更多的層,并驅(qū)動(dòng)了對(duì)微過孔高密度互連(HDI)技術(shù)的需求。

HDI是為了響應(yīng)上述需求而開發(fā)的互連技術(shù)。微過孔與超薄電介質(zhì)、更細(xì)的走線和更小的線間距是HDI技術(shù)的主要特徵。

2.RF設(shè)計(jì)

針對(duì)RF設(shè)計(jì),RF電路應(yīng)該直接設(shè)計(jì)成系統(tǒng)原理圖和系統(tǒng)板布局,而不用于進(jìn)行后續(xù)轉(zhuǎn)換的分離環(huán)境。RF模擬環(huán)境裝的所有模擬、調(diào)諧和最佳化能力仍然是必須的,但模擬環(huán)境較‘實(shí)際’的設(shè)計(jì)卻能接受更為原始的數(shù)據(jù)。因此,數(shù)據(jù)模型間的差異,以及由此引起的設(shè)計(jì)轉(zhuǎn)換問題將會(huì)銷聲匿跡。首先,設(shè)計(jì)者可在系統(tǒng)設(shè)計(jì)與RF模擬之間直接互動(dòng);其次,如果設(shè)計(jì)師進(jìn)行一個(gè)大規(guī)模或相當(dāng)復(fù)雜的RF設(shè)計(jì),他們可能想將電路模擬任務(wù)分配到平行執(zhí)行的多個(gè)運(yùn)算平臺(tái),或者他們想將一個(gè)由多個(gè)模組組成的設(shè)計(jì)中每一個(gè)電路發(fā)送到各自的模擬器中,以縮短模擬時(shí)間。

3.先進(jìn)的封裝

現(xiàn)代產(chǎn)品日漸增加的功能復(fù)雜性要求被動(dòng)元件的數(shù)量也相應(yīng)增加,主要體現(xiàn)在低功耗、高頻應(yīng)用中的去藕電容器和終端匹配電阻數(shù)量的增加。雖然被動(dòng)表貼元件的封裝在歷經(jīng)數(shù)年后已縮小得相當(dāng)可觀了,但在試圖獲得最大極限密度時(shí)其結(jié)果仍然是相同的。印刷零組件技術(shù)使得從多晶片組件(MCM)和混合組件轉(zhuǎn)變到今天直接可以作為嵌入式被動(dòng)元件的SiP和PCB。在轉(zhuǎn)變的過程中採(cǎi)用了最新的裝配技術(shù)。例如,在一個(gè)層狀結(jié)構(gòu)中包含了一個(gè)阻抗材料層,以及直接在微球柵陣列(uBGA)封裝下面採(cǎi)用了串聯(lián)終端電阻,這些都大幅提高了電路的性能。現(xiàn)在,嵌入式被動(dòng)元件可獲得高精密度的設(shè)計(jì),因而省去了雷射清潔焊縫的額外加工步驟。無線組件中也正朝著直接在基板內(nèi)提高整合度的方向發(fā)展。

4.剛性柔性PCB

為了設(shè)計(jì)一個(gè)剛性柔性PCB,必須考慮影響裝配過程的所有因素。設(shè)計(jì)者不能像設(shè)計(jì)一個(gè)剛性PCB那樣來簡(jiǎn)單地設(shè)計(jì)一個(gè)剛性柔性PCB。他們必須管理設(shè)計(jì)彎曲區(qū)域,以確保設(shè)計(jì)要點(diǎn)將不會(huì)由于彎曲面的應(yīng)力作用而使得導(dǎo)體斷裂和剝離。仍有許多機(jī)械因素需要考慮,如最小彎曲半徑、電介質(zhì)厚度和類型、金屬片重量、銅電鍍、整體電路厚度、層數(shù)和彎曲部份數(shù)量。

理解剛性柔性設(shè)計(jì)并決定你的產(chǎn)品是否允許你制作一個(gè)剛性柔性設(shè)計(jì)。

5.訊號(hào)完整性規(guī)劃

最近幾年,針對(duì)Serdes轉(zhuǎn)換,或串列互連、平行匯流排結(jié)構(gòu)和差分對(duì)結(jié)構(gòu)相關(guān)的新技術(shù)一直不斷進(jìn)步。

圖2顯示了針對(duì)一個(gè)平行匯流排和Serdes轉(zhuǎn)換設(shè)計(jì)所遇到的典型設(shè)計(jì)問題。平行匯流排設(shè)計(jì)侷限在系統(tǒng)時(shí)序的變化,如時(shí)脈歪斜和傳播延遲。由于整個(gè)匯流排寬度上的時(shí)脈歪斜,針對(duì)時(shí)序約束的設(shè)計(jì)依然是困難的。增加時(shí)脈速率只會(huì)讓問題變得更糟糕。

另一方面,差分對(duì)結(jié)構(gòu)在硬體層面採(cǎi)用了一個(gè)可交換的點(diǎn)對(duì)點(diǎn)連接來實(shí)現(xiàn)串列通訊。通常,它透過一個(gè)單向串列‘通道’來轉(zhuǎn)移數(shù)據(jù),這個(gè)單向串列通道可迭加成1-、2-、4-、8-、16-和32-寬度的配置。每個(gè)通道攜帶一個(gè)位元組的數(shù)據(jù),匯流排可處理從8位元組到256位元組的數(shù)據(jù)寬度,并透過使用某些形式的錯(cuò)誤檢測(cè)技巧來保持?jǐn)?shù)據(jù)完整性。然而,更高的數(shù)據(jù)率導(dǎo)致了其他設(shè)計(jì)問題。高頻下的時(shí)脈恢復(fù)成為系統(tǒng)的重?fù)?dān),因?yàn)闀r(shí)脈要快速鎖定輸入數(shù)據(jù)串流,以及為了提高電路的抗抖性能,還要減少所有週期到週期間的抖動(dòng)。電源噪音也為設(shè)計(jì)師帶來了額外問題。該類型的噪音增加了產(chǎn)生嚴(yán)重抖動(dòng)的可能,這將使得視圖的開眼變得更加困難。另外的挑戰(zhàn)是減少共模噪音,解決來自于IC封裝、PCB板、電纜和連接器的損耗效應(yīng)所導(dǎo)致的問題。

6.設(shè)計(jì)套件的實(shí)用性

USB、DDR/DDR2、PCI-X、PCI-Express和RocketIO等設(shè)計(jì)套件將毋庸置疑地對(duì)設(shè)計(jì)師進(jìn)軍新技術(shù)領(lǐng)域產(chǎn)生很大的幫助。設(shè)計(jì)套件提供了技術(shù)的概況、詳細(xì)說明以及設(shè)計(jì)者將要面臨的困難,并提供模擬及如何制作布線約束等資訊。它與程式共同提供說明文件,為設(shè)計(jì)者提供了一個(gè)掌握先進(jìn)新技術(shù)的先機(jī)。

看來,要獲得一個(gè)能處理布局的PCB工具是容易的;但獲得一個(gè)不僅能滿足布局而且能解決迫切需求的工具才是至關(guān)重要的。

深圳宏力捷推薦服務(wù):PCB設(shè)計(jì)打樣 | PCB抄板打樣 | PCB打樣&批量生產(chǎn) | PCBA代工代料