SIR (Surface Insulation Resistance) 通常用來作

電路板的信賴性試驗,其方法為在印刷電路板(PCB)上將成對的電極交錯連接成梳形電路(Pattern),并印上錫膏(solder paste),然后在一定高溫高濕的環境下持續地給予一定偏壓(BIAS VOLTAGE),經過一定長時間的試驗(24H,48H,96H,168H)并觀察線路間是否有瞬間短路或出現絕緣失效的緩慢漏電情形發生。

這個試驗也有助看出錫膏中的助焊劑或其他化學物品在PCB板面上是否有殘留任何會影響電子零件電氣特性的物質。一般我們使用這個方法來量測靜態的表面絕緣電阻(SIR)與動態的離子遷移現象(ION MIGRATION),另外,它也可以拿來作 CAF(Conductive Anodic Filament,導電性細絲物,陽極性玻纖纖維之漏電現象)試驗。

注:CAF主要在測試助焊劑對PCB板吸濕性及玻璃纖維表面分離的影響。

表面絕緣電阻(SIR)被廣泛用來評估污染物對組裝件可靠度的影響。跟其他方法相比,SIR的優點除了可偵測局部的污染外,也可以測得離子及非離子污染物對印刷電路板(PCB)可靠度的影響,其效果遠比其他方法(如清潔度試驗、鉻酸銀試驗…等)來的有效及方便。

由于現在的

電路板布線越來越密,焊點與焊點也越來越近,所以這項實驗也可作為錫膏助焊劑的可用性評估參考。

Comb Pattern,梳形電路是一種「多指狀」互相交錯的密集線路圖形,可用在板面清潔度、綠漆絕緣性等進行高電壓測試的一種特殊線路圖形。

SIR 量測標淮:IPC-TM-650

▼SIR實驗用的測試板,一片板子有四組成對的電極交錯連接成梳形圖案(Pattern)

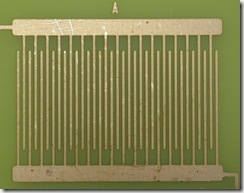

▼單獨把一組SIR實驗用成對的電極交錯連接成梳形圖案(Pattern)放大圖

量測SIR時要在梳形圖案(Pattern)上印上錫膏,然后垂直放入已印有錫膏的SIR測試板并置于環境試驗機中,還要在其正、負極加上 45~50VDC 的偏壓,環境實驗的條件如下:

85+/-2℃ + 20%RH 3小時

↓ 至少15分鐘

85+/-2℃ + 85%RH 至少1小時后開始加 50VDC 偏壓

↓ 24小時后用 100VDC 量測 SIR 值

↓ 再24小時后用 100VDC 再量測 SIR 值 (共48小時)

↓ 再48小時后用 100VDC 再量測 SIR 值 (共96小時)

↓ 再96小時后用 100VDC 再量測 SIR 值 (共168小時)

每隔一段時間紀錄SIR的變化。

深圳宏力捷推薦服務:PCB設計打樣 | PCB抄板打樣 | PCB打樣&批量生產 | PCBA代工代料