W(設計線寬)該因素一般情況下是由客戶決定的。

但在

PCB設計時請充分考慮線寬對該阻抗值的配合性,即為達到該阻抗值在一定的H、Er和使用頻率等條件下線寬的使用是有一定的限制的。

當然阻抗控制不僅僅是上述幾因素,上面所提的只是比較而言影響度較大的幾因素,也是從PCB制造廠商的角度來看待該問題的。

以下是我們在高多層PCB實際生產加工過程中,總結出來的一些高多層PCB的結構示例,但必須說明的是:

這僅僅是一點,不足以說明一面的問題,僅僅是建設性的參考。

由于時間和篇幅的限制在此處沒能將一些目前已經成為趨勢的做法列出如內層使用H/H(半 Oz )銅箔、Low DK材料……

其中的一些數值是比較粗略的計算結果,實際運用時還需根據實際的情況進行細化。

考慮到客戶的需求基本上還是——高多層能薄一點,因此在高層的結構中我們盡可能的舉厚度比較適中的結構。

20層以上由于結構更加復雜,同時是客戶與我們共同努力的結果,因此在實際加工的過程中,根據客戶的具體要求再做具體的探討。如24層 6mm、30層6--8mm…...

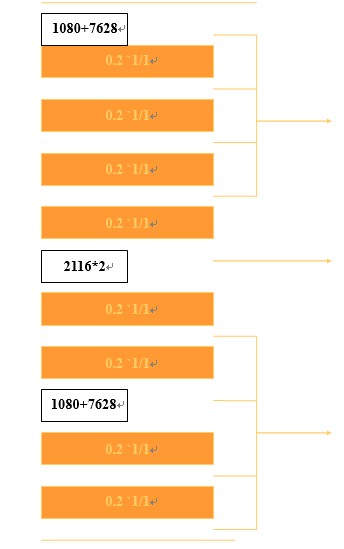

2.0mm 8層PCB板的通常配置

? 1080+7628

? 1080+7628

? 1080+7628

? 1080+7628

其阻抗值一般為兩種情況:

? Microstrip Line=8mil Zo=70 左右

? Offset Stripline 有兩種可能:

1. Line=8mil Zo=45 左右

2. Line=8mil Zo=50 左右

3. 如為背板的設計則還有另一種情況

針對不同的需要可以對左示的結構進行更改而得。

3.0mm 8層PCB板的通常配置

? 1080+7628*2

? 7628*2

? 7628*2

? 1080+7628*2

其阻抗值一般為兩種情況:

? Microstrip Line=8mil Zo=80 左右

? Offset Stripline 有兩種可能:

1. Line=8mil Zo=58 左右

2. Line=8mil Zo=68 左右

3.如為背板的設計則還有另一種情況

針對不同的需要可以對左示的結構進行更改而得。

2.0mm 10層PCB板的通常配置

? 1080+7628

? 7628+1080

? 1080*2

? 7658+1080

? 1080+7628

其阻抗值一般為以下幾種情況:

? Microstrip Line=8mil Zo=70 左右

? Offset Stripline 有兩種可能:

1. Line=8mil Zo=33 左右

2. Line=8mil Zo=47 左右

3.如為背板的設計已經調整內部地電的排列還有其他的一些情況出現。

針對Stripline Zo偏小的情況一般是壓縮Microstrip 的介質厚度來增加Stripline的介質厚度滿足Zo的需求。

針對不同的需要可以對左示的結構進行更改而得。

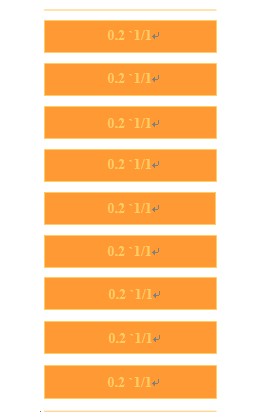

2.0mm 12層PCB板的通常配置

? 1080*2

? 1080*2

? 1080*2

? 1080*2

? 1080*2

? 1080*2

其阻抗值一般為以下幾種情況:

? Microstrip Line=8mil Zo=50 左右

? Offset Stripline 有兩種可能:

1. Line=8mil Zo=30 左右

2. Line=8mil Zo=33 左右

3.如為背板的設計以及調整內部地電的排列還有其他的一些情況出現。

針對Stripline Zo偏小的情況一般是增加Stripline的介質厚度滿足Zo 的需求,通常50ohm的需求該種板會在3.0mm厚度。

針對不同的需要可以對左示的結構進行更改而得。

3.0mm 14層PCB板的通常配置

? 1080+7628

? 1080+7628

? 1080+7628

? 1080+7628

? 1080+7628

? 1080+7628

? 1080+7628

其阻抗值一般為以下幾種情況:

? Microstrip Line=8mil Zo=70 左右

? Offset Stripline 有兩種可能:

1. Line=8mil Zo=33 左右

2. Line=8mil Zo=40 左右

3.如調整內部地電的排列還有其他的一些情況出現。

針對Stripline Zo偏小的情況一般是縮小Microstrip 的介質厚度,同時縮小地地或電電之間的介質厚度來增加Stripline的介質厚度滿足Zo的需求,包括采用不同厚度芯板進行壓合的方法。

針對不同的需要可以對左示的結構進行更改而得。

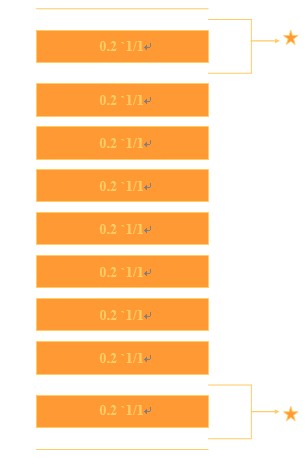

16層 3.0mm電路板的結構

? 1080+2116

? 1080+2116

? 2116*2

? 2116*2

? 2116*2

? 2116*2

? 1080+2116

? 1080+2116

其阻抗值一般為以下幾種情況:

? Microstrip Line=8mil Zo=60 左右

? Offset Stripline 有幾種可能:

當Line=8mil時 Zo值在33--50…

如調整內部地電的排列還有其他的一些情況出現。

針對Stripline Zo偏小的情況一般Backboard設計 Top&Bom層是無Microstrip 要求,因此調整它們的介質厚度,調整地地或電電之間的介質厚度來增加Stripline的介質厚度滿足Zo 的需求,包括采用不同厚度芯板進行壓合的方法。

針對不同的需要可以對左示的結構進行更改。

18層 3.0mm厚度電路板的結構

? 各層之間的半固化片全部使用1080*2

從此種結構的特性上來看Microstrip

Line=8mil Zo=50 左右比較符合常規要求,但Offset Stripline 則可能太小。

針對Stripline Zo偏小的情況,一般Backboard設計 Top&Bom層是無Microstrip 要求,因此調整它們的介質厚度,調整地地或電電之間的介質厚度來增加Stripline的介質厚度滿足Zo 的需求。

包括采用不同厚度芯板進行壓合的方法通過局部的調整來滿足要求。

針對不同的需要可以對左示的結構進行更改。

18層 3.8mm厚度電路板的結構

? 1080+7628

? 2116*2

? 1080+7628

從此種結構的特性上來看Microstrip Line=8mil Zo=70 左右,比一般常規的要求偏大,但Offset Stripline 則可能偏小。

針對Stripline Zo偏小的情況,一般Backboard設計 Top&Bom層是無Microstrip 要求,因此調整它們的介質厚度,調整地地或電電之間的介質厚度來增加Stripline的介質厚度滿足Zo 的需求。

包括采用不同厚度芯板進行壓合的方法通過局部的調整來滿足要求。

針對不同的需要可以對左示的結構進行更改。

20層 3.0--3.2mm厚度電路板的結構

? 各層之間的半固化片全部使用1080*2

此種結構阻抗的狀況和調整方法與18層3.0mm的情況基本相同,主要的問題是Stripline偏小。

20層 4.0mm左右厚度電路板的結構

? 標注的地方為1080+2116,其馀的結構為1080+7628

從此種結構的特性上來看,一般情況是屬于backboard的設計因此Microstrip就沒了,Offset Stripline 的Zo=33--50(依舊設計的層次排列)如想得到50則在設計上一定要處理好一些問題,且并非每個信號層都能控制到。

針對不同的需要可以對左示的結構進行更改。

? 為使有阻抗要求的PCB在生產加工過程中能得以順利的完成,故我們建議雙方在合作的過程應中注意以下幾方面的協作和溝通。

? 如貴公司的PCB有阻抗控制的要求,則貴公司在提供電路板加工資料時請提供有阻抗要求的該線條的位置、設計線寬、阻抗值、相對應的介質層厚度……相關的參數。

? 如為差動阻抗還需提供差分線之間的間距。

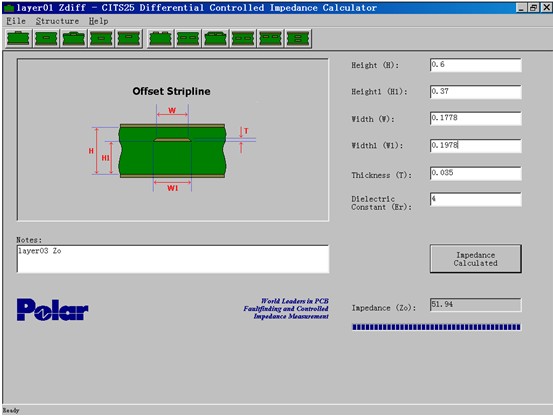

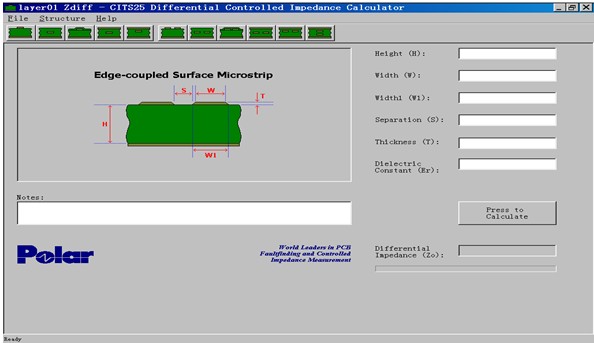

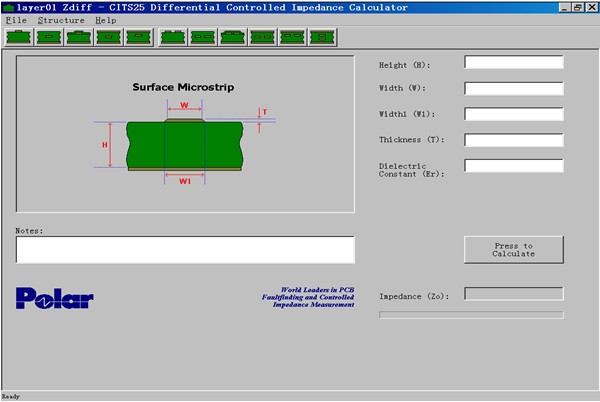

? 我們收到貴公司的資料之后,將用POLAR CITS25軟體進行核算,如發現有偏差,我們將及時通知客戶,同時在取得客戶同意的條件下對上述各參數進行調整以達到滿足阻抗值的要求。

? 如該PCB其本身的性能是比較特殊的如:RF(射頻)板等,在資料中敬請予以說明,因為該類板是不能以改動線寬來滿足阻抗值的。

? 以上所述僅是我們處于PCB制作廠商的角度,對阻抗的加工、品質控制方面的一些淺薄認識,其必然有很多疏漏之處,敬請諒解。

? “阻抗控制”在PCB業界來講是一個比較復雜,相對較新的課題,因此在合作的過程中,相互的交流、協作是第一性的,我們忠實于客戶的設計,但不局限。

深圳宏力捷推薦服務:PCB設計打樣 | PCB抄板打樣 | PCB打樣&批量生產 | PCBA代工代料