二、走線原則

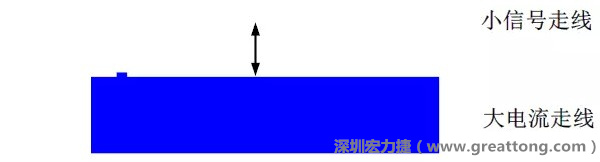

1、小信號走線要盡量遠離大電流走線,兩者不要靠近平行走線,如果無法避免平行的話,也要拉開足夠的距離,避免小信號走線受到干擾。

圖6

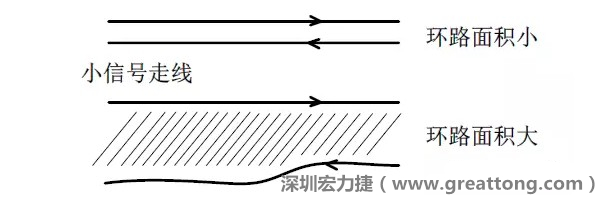

2、關鍵的小信號走線,如電流取樣信號線和光耦反饋的信號線等,盡量減小回路包圍的面積。

圖7

3、相鄰之間不應有過長的平行線(當然同一電流回路平行走線是可以的),上下層走線盡量采用交叉用垂直方式,走線不要突然拐角(即:≤90°),直角、銳角在高頻電路中會影響電氣性能。

圖8

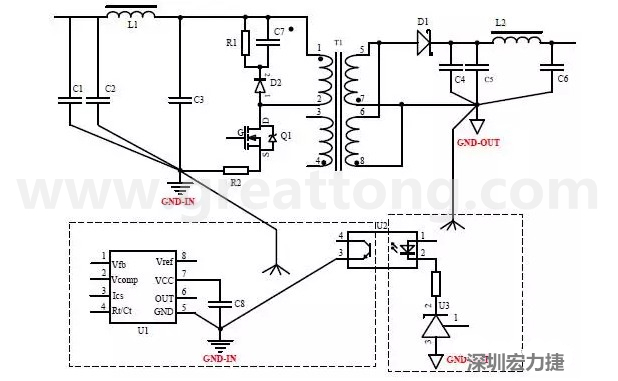

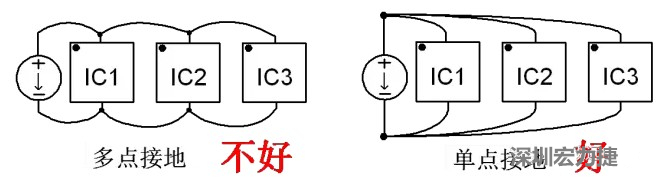

4、功率回路和控制回路要注意分開,采用單點接地方式,如圖9和圖10所示。

初級PWM控制IC周圍的元件接地接至IC的地腳,再從地腳引出至大電容地線,然后與功率地連接。次級TL431周圍的元件接地至TL431的3腳,再與輸出電容的地連接。多個IC的情況,采用并聯單點接地的方式。

圖9

圖10

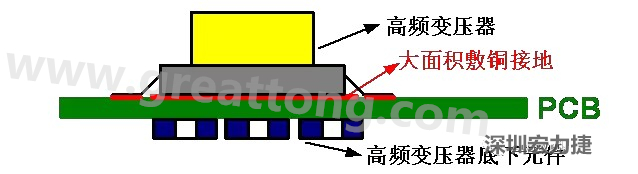

5、高頻元件(如變壓器、電感)底下第一層不要走線,高頻元件正對著的底面也最好不要放置元件,如果無法避免,可以采用屏蔽的方式,例如高頻元件在Top層,控制電路正對著在Bottom層,注意要在高頻元件所在的第一層敷銅進行屏蔽,如圖11所示,這樣可以避免高頻噪聲輻射干擾到底面的控制電路。

圖11

6、濾波電容的走線要特別注意,如圖12,左圖有一部分紋波&噪聲會經過走線出去,右圖濾波效果會好很多,紋波&噪聲經過濾波電容被完全濾掉。

圖12

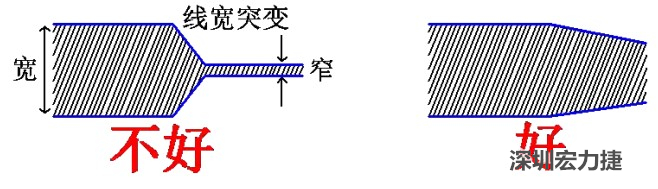

7、電源線、地線盡量靠近,以減小所包圍的面積,從而減小外界磁場環路切割產生的電磁干擾,同時減少環路對外的電磁輻射。電源線、地線的布線盡量加粗縮短,以減小環路電阻,轉角要圓滑,線寬不要突變,如圖13所示。

圖13

8、發熱大的元件(如TO-252封裝的MOS管)下可以大面積裸銅,用于散熱,這樣可以提高元件的可靠性。功率走線銅箔較窄處可以裸銅用于加錫以保證大電流的流通。

三、安規距離與工藝要求

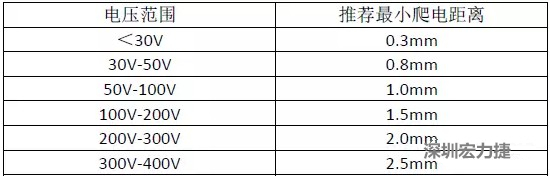

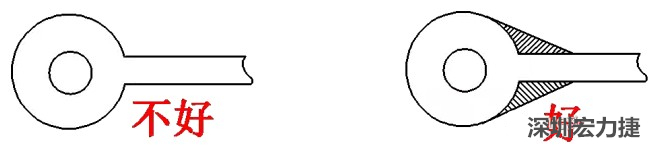

1、電氣間隙:兩相鄰導體或一個導體與相鄰導電機殼表面的沿空氣測量的最短距離。爬電距離:兩相鄰導體或一個導體與相鄰導電機殼表面的沿著絕緣表面測量的最短距離。如果碰到模塊PCB空間有限,爬電距離不夠,可以采用開槽的方式,如圖14所示,在光耦處開隔離槽以滿足初次級良好隔離。一般最小開槽寬度為1mm,如果要開更小的槽(如0.6mm,0.8mm),一般需要特殊說明,找加工精度高的PCB廠家才行,當然費用也會增加。

圖14

一般電源模塊電壓與最小爬電距離的關系可參照下表:

2、元件到板邊的距離要求。位于電路板邊緣的元器件,離電路板邊緣一般不少于2mm,對于像10W以下的小型化DC-DC模塊,由于元件體積和高度比較小,而且輸入輸出電壓不高,為了滿足小型化的要求,也要至少留有0.5mm以上的距離。大面積銅箔到外框的距離應至少保證0.20mm以上的間距,因在銑外形時容易銑到銅箔上造成銅箔翹起及由其引起焊劑脫落問題。

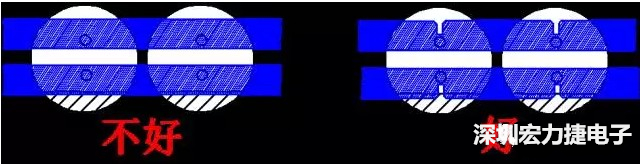

3、若走線入圓焊盤或過孔的寬度較圓焊盤的直徑小時,則需加淚滴,加強吸附力,避免焊盤或過孔脫落。

圖15

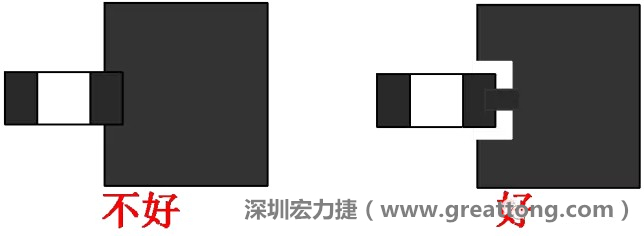

4、SMD器件的引腳與大面積銅箔連接時,要進行熱隔離處理,不然過回流焊的時候由于散熱快,容易造成虛焊或脫焊。

圖16

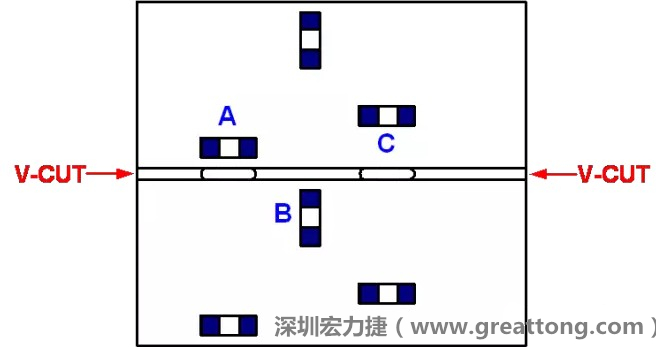

5、PCB拼板的時候,要考慮分板可行性,確保元件離板邊的距離要足夠,同時還要考慮分板的應力會不會造成元件的脫翹。如圖17所示,可以適當的開槽,減小分斷PCB時的應力,元件A擺放的位置與V-CUT槽方向平行,分斷時應力比元件B小;元件C比元件A遠離V-CUT槽,分斷時應力也比元件A的小。

圖17

當然,以上只是個人總結的一些開關電源PCB設計的經驗,還有很多細節上的或其他方面的知識需要注意的,最后我想說的是PCB設計,除了原則要求和經驗知識之外,最重要的一點是細心再細心,檢查再檢查。

深圳宏力捷推薦服務:PCB設計打樣 | PCB抄板打樣 | PCB打樣&批量生產 | PCBA代工代料